- 您现在的位置:买卖IC网 > Sheet目录477 > MICRF219AYQS TR (Micrel Inc)IC RECEIVER QWIKRADIO 16QSOP

Micrel

MICRF219

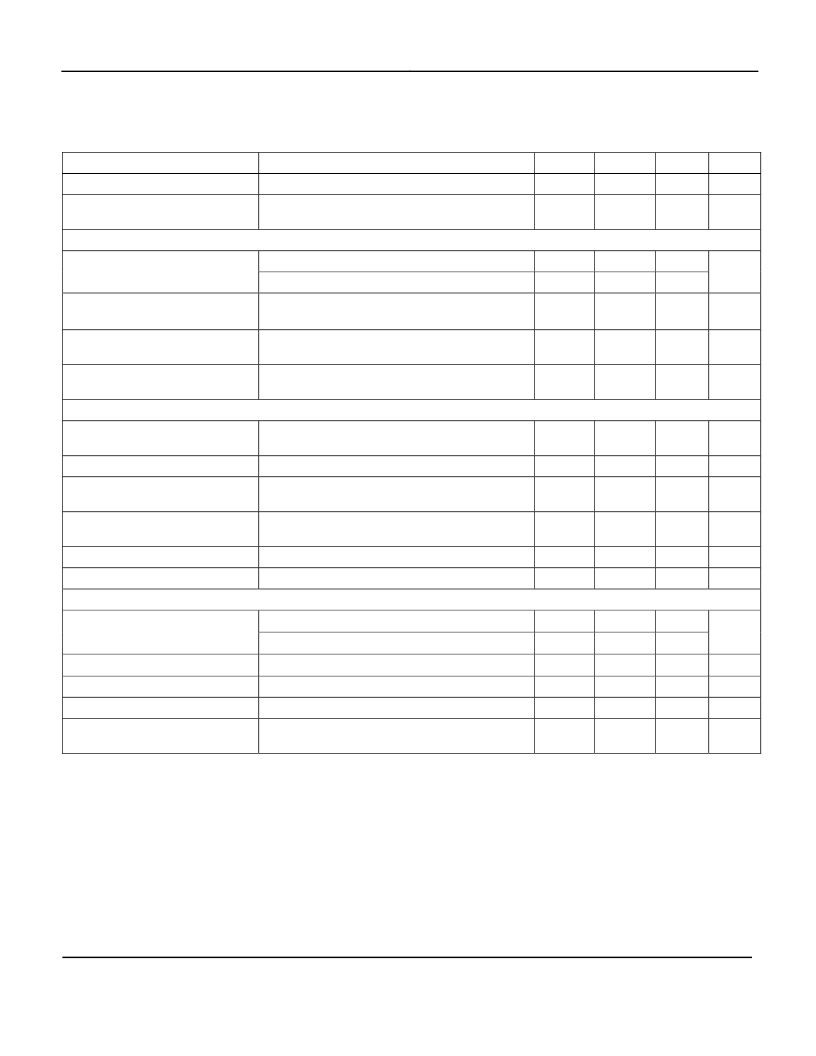

Electrical Characteristics (Continued)

Specifications apply for V DD = 3.3V, GN D = 0V, C AGC = 4.7μF, C TH = 0.1μ F, f R X = 433.92 M Hz un le ss oth erwise noted. Bold values

indicate –40 ° C – T A – 105 ° C. 1kbps data rate (Manchester encoded), refer ence oscill ator frequenc y = 13 .52127MHz.

Parameter

Conditi on

Min.

Typ.

Max.

Units

Reference Oscillator Input Range

Reference Oscillator Sourc e

Current

V(REFOSC ) = 0V

0.2

300

1.5

V P-P

μA

Demodulator

CTH Source Impedance

CTH Leakage Current

F REFOSC = 9.81563 MHz

F REFOSC = 13.52127MH z

T A = 25oC

T A = +105oC

165

120

± 2

± 800

k ?

nA

Demodulator Filter Bandwid th

@ 315MHz

Demodulator Filter Bandwi dth

@ 434MHz

Programmable , see application section

Programmabl e, see application section

117 0

1 625

9400

13000

Hz

Hz

Digital / Control Functions

DO Pin Output Current

Output Rise And Fall Times

Input High Voltage

Input Low Voltage

Output Voltage High

Output Voltage Low

As output source @ 0.8 V DD

sink @ 0.2 V DD

CI = 15pF, pin DO, 10-90%

Pins SCLK, DO (As input), SHDN,SEL0,

SEL1,SQ

Pins SCLK, DO (As input), SHDN, SEL0,

SEL1,SQ

DO

DO

0.8V DD

0.8V DD

260

600

2

0.2V DD

0.2V DD

μA

μsec

V

V

V

V

RSSI

RSSI DC Output Voltage Range

RSSI Response Slope

RSSI Output Current

RSSI Output Impedance

RSSI Response Time

? 100dBm

? 40dBm

? 110dBm to -40dBm

50% data duty cycle, input power to Antenna = -

20dBm

0.4

2.0

25

400

250

0.3

V

mV/dB

μA

?

sec

Notes:

1.

2.

3.

4.

5.

Exc eeding the absolute maximum rating may damage the device.

The device is not guaranteed to function outside of its operating rating.

Device is ESD sensitive. Use appropriate ESD precautions. Exceeding the absolute maximum rating may damage the device.

Sensitivity is defined as the average signal level measured at the input necessary to achieve 10 -2 BER (bit error rate). The input signal is defined

as a return-to-zero (RZ) waveform with 50% average duty cycle (Manchester encoded) at a data rate of 1kbps.

When data burst does not contain preamble, duty cycle is defined as total duty cycle, including any “quiet” time between data bursts. When data

bursts contain preamble sufficient to charge the slice level on capacitor C TH , then duty cycle is the effective duty cycle of the burst alone. [For

example, 100msec burst with 50% duty cycle, and 100msec “quiet” time between bursts. If burst includes preamble, duty cycle is

T ON /(T ON +t OFF )= 50%; without preamble, duty cycle is T ON /(T ON + T OFF + T QUIET ) = 50msec/(200msec)=25%. T ON is the (Average number of

1’s/burst) × bit time, and T OFF = (T BURST – T ON .)

June 2011

4

M9999-060811

(408) 944-0800

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

MICRF220AYQS TR

RCVR ASK/OOK 300-450MHZ 16QSOP

MICRF221AYQS TR

IC RF RECEIVER QWIKRADIO 16-QSOP

MICRF300YC6 TR

IC AMP 100/1000MHZ LN SC70-6

MICRF500BLQTR

TXRX UHF 700-1100MHZ 44-LQFP

MICRF501BLQ TR

TXRX SGL 300-600MHZ 44-LQFP

MICRF505DEV1

KIT DEV RADIOWIRE 850-950MHZ

MICRF506DEV1

EVAL BOARD EXPERIMENTAL MICRF506

MICRF507YML TR

TXRX FSK LOW PWR W/AMP 32MLF

相关代理商/技术参数

MICRF220

制造商:MICREL 制造商全称:Micrel Semiconductor 功能描述:300MHz to 450MHz, 3.3V ASK/OOK Receiver with RSSI and Squelch

MICRF220-315-EV

功能描述:EVAL BOARD FOR MICRF220 制造商:microchip technology 系列:- 零件状态:有效 类型:接收器 频率:315MHz 配套使用产品/相关产品:MICRF220 所含物品:板 标准包装:1

MICRF220-433-EV

功能描述:EVAL BOARD FOR MICRF220 制造商:microchip technology 系列:- 零件状态:有效 类型:接收器 频率:433.92MHz 配套使用产品/相关产品:MICRF220 所含物品:板 标准包装:1

MICRF220AYQS

功能描述:射频接收器 300MHz to 450MHz, 3.0V to 3.6V, 6mA, <10kbps ASK Receiver with RSSI and Shutdown

RoHS:否 制造商:Skyworks Solutions, Inc. 类型:GPS Receiver 封装 / 箱体:QFN-24 工作频率:4.092 MHz 工作电源电压:3.3 V 封装:Reel

MICRF220AYQS TR

功能描述:射频接收器 300MHz to 450MHz, 3.0V to 3.6V, 6mA, <10kbps ASK Receiver with RSSI and Shutdown

RoHS:否 制造商:Skyworks Solutions, Inc. 类型:GPS Receiver 封装 / 箱体:QFN-24 工作频率:4.092 MHz 工作电源电压:3.3 V 封装:Reel

MICRF221

制造商:MICREL 制造商全称:Micrel Semiconductor 功能描述:3.3V, QwikRadio 850 MHz to 950 MHz Receiver

MICRF221AYQS

功能描述:射频接收器 850MHz to 950MHz, 3.0V to 3.6V, 9mA, 10kbps ASK Recdeiver with Auto-Poll and RSSI, Shutdown in 16-lead QSOP

RoHS:否 制造商:Skyworks Solutions, Inc. 类型:GPS Receiver 封装 / 箱体:QFN-24 工作频率:4.092 MHz 工作电源电压:3.3 V 封装:Reel

MICRF221AYQS TR

功能描述:射频接收器 850MHz to 950MHz, 3.0V to 3.6V, 9mA, 10kbps ASK Recdeiver with Auto-Poll and RSSI, Shutdown in 16-lead QSOP

RoHS:否 制造商:Skyworks Solutions, Inc. 类型:GPS Receiver 封装 / 箱体:QFN-24 工作频率:4.092 MHz 工作电源电压:3.3 V 封装:Reel